Famílias de Circuitos Lógicos

Introdução

Até aqui, utilizamos os blocos lógicos sem nos preocuparmos com suas estruturas internas.Dedicaremos este capítulo ao estudo das principais famílias de circuitos lógicos utilizadas atualmente.

Entende-se por famílias de circuitos lógicos, os tipos de estruturas internas que nos permitem a confecção destes blocos em circuitos integrados. Cada família lógica utiliza determinados componentes em seus blocos e, de acordo com estes, a família possuirá determinadas características relacionadas ao seu funcionamento e desempenho prático.

As famílias utilizadas atualmente dentro da área de Eletrônica Digital são a TTL (Transistor- Transistor Logic) e a CMOS (Complementary Metal Oxide Semiconductor), porém derivam de uma série de famílias lógicas, hoje obsoletas. A seguir, vamos relacionar em escala tecnológica evolutiva, algumas famílias utilizadas anteriormente, precedentes à família TTL.

- DCTL (Direct-Coupled Transistor Logic)

- RTL (Resistor-Transistor Logic)

- RCTL (Resistor-Capacitor Transistor Logic)

- DTL (Diode-Transistor Logic)

- HTL (High-Thereshold Logic)

- ECL (Emitter-Coupled Logic)

O estudo das características da maioria destas famílias citadas não faz sentido nos dias de hoje, a não ser que seja feito com aspectos de evolução histórica, mostrando a origem construtiva da tecnologia atual.

A família ECL, em particular, embora não tenha sido desenvolvida na atualidade, ainda é utilizada devido principalmente ao seu comportamento frente a situações que exigem alta velocidade de operação, característica típica desta família, sendo, porém, seu emprego restrito a aplicações específicas, não se caracterizando mais em série comercial.

Estudaremos, mais adiante, as famílias TTL e CMOS, e as respectivas versões derivadas. Primeiramente, vamos abordar alguns conceitos básicos para melhor compreensão e avaliação das

mesmas.

Conceitos e Parâmetros das Famílias Lógicas

Nos itens subsequentes, vamos abordar os principais conceitos envolvidos no estudo das famílias de circuitos lógicos. São tópicos que caracterizam parâmetros como os níveis de tensão e de corrente de entrada e saída, quantidades de blocos a serem conectados, tempo de resposta do bloco e seu fator de imunidade ao ruído. O primeiro a ser abordado é relativo aos níveis de tensão e de corrente.

Níveis de Tensão e de Corrente

No capítulo 2, definimos nível 1 e nível 0. Na realidade, esses níveis irão variar dentro de faixas. O nível 0 não precisa ser necessariamente 0, mas, sim, uma tensão pequena abaixo de um certo valor máximo. O nível 1, como foi definido, representa uma tensão, mas não precisa ser necessariamente um valor e, sim, uma faixa acima de um valor mínimo e abaixo de um valor máximo. Conforme a tecnologia de construção do circuito interno, cada família ou versão derivada irá possuir uma faixa de trabalho para esses níveis, sendo especificações diferentes para entrada e saída do bloco.

Outro parâmetro é o que trata da corrente. Quando um nível lógico 1 for aplicado a uma entrada de um bloco lógico, esta irá consumir uma corrente. O mesmo ocorre quando a saída de um bloco lógico

em nível 1 for conectada à entrada de outro. Haverá uma drenagem de corrente, na prática limitada.

Da mesma forma, se for aplicado o nível 0 (potencial de terra) à entrada de um bloco lógico, haverá uma deriva de corrente, no sentido do bloco para o terminal, originada conforme as características do circuito do bloco.

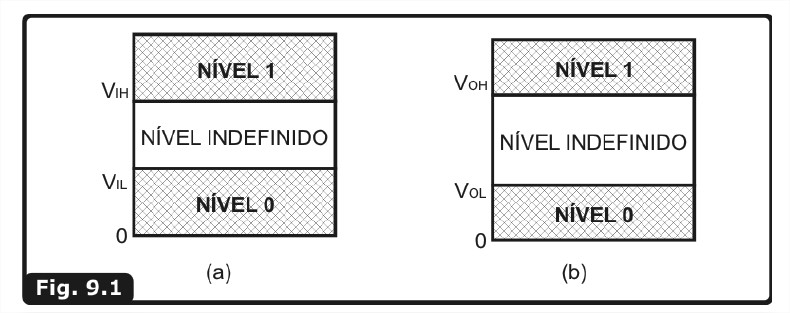

Notamos que na região compreendida entre o valor máximo de nível 0 (VIL E VOL), e o valormínimo de nível 1 (VIH e VOH) o nível lógico será indefinido. Para existir compatibilidade com segurança entre entrada e saída na família, é necessário que VOL seja menor que VIL, e que VOH seja maior que VIH.

Fan-Out

Até agora, trabalhamos com os blocos lógicos sem nos preocuparmos com o número de conexões feitas nas saídas. Na prática, existe um parâmetro denominado, em inglês, de Fan-Out (feixe de saída), que estipula o limite dessas ligações.

Definimos Fan-Out como sendo o número máximo de blocos lógicos que pode ser ligado à saída de outro da mesma família. Embora esta definição seja em nível de mesma família, este fator pode ser determinado entre famílias e versões compatíveis.

Se este fator for excedido na ligação da saída de um bloco às entradas de outros, os limites máximos de corrente serão ultrapassados, acarretando principalmente a queda do nível 1 de saída.

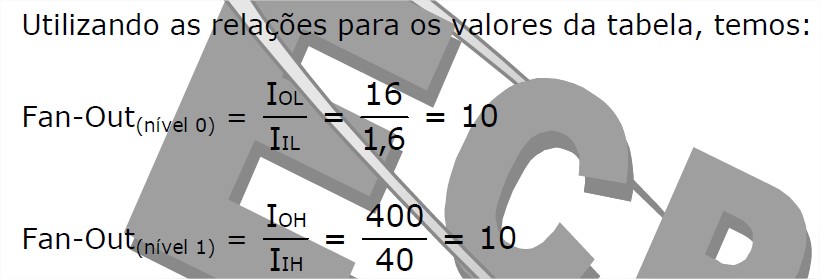

O Fan-Out está relacionado com as correntes máximas de saída e de entrada dos blocos lógicos, podendo ser determinado no nível 0 e no nível 1. A seguir, vamos escrever as relações para estes cálculos:

Por sua vez, em nível 0, irá também absorver uma corrente originária da entrada do bloco seguinte conectado.

Existe uma terminologia padrão empregada pelos principais fabricantes de circuitos integrados nos respectivos manuais, para designar estes parâmetros. Vamos apresentá-los e defini-los, a seguir:

- VIL (Low-Level Input Voltage): valor de tensão (máxima), que garante o nível 0 na entrada.

- VOL (Low-Level Output Voltage): valor de tensão (máxima), que garante o nível 0 na saída.

- VIH (High-Level Input Voltage): valor de tensão (mínima), que garante o nível 1 na entrada.

- VOH (High-Level Output Voltage): valor de tensão (mínima), que garante o nível 1 na saída.

- IIL (Low-Level Input Current): valor de corrente (máxima), no terminal de entrada (no sentido do bloco para o terminal), quando é aplicado o nível 0.

- IOL (Low-Level Output Current): valor de corrente (máxima), que a saída pode receber quando é aplicado nível 0.

- IIH (High-Level Input Current): valor de corrente de entrada (máxima), quando é aplicado nível 1.

- IOH (High-Level Output Current): valor de corrente de saída (máxima), quando é aplicado nível 1.

Nos manuais, além dos limites de mínimo e máximo, conforme a definição do parâmetro, são encontrados os valores típicos de trabalho.

A figura 9.1, apresenta os diagramas relativos aos níveis de tensão definidos, tanto para entrada(a), como para saída (b), de um mesmo bloco lógico.

Os valores de corrente utilizados nas relações nas relações são extraídos dos manuais comerciais.

Na prática, os fabricantes de circuitos integrados, normalmente, generalizam o valor obtido para um só, válido para toda a família lógica, porém pode haver variação deste valor conforme a versão lógica utilizada.

Para exemplificar este procedimento, vamos calcular estes parâmetros para os blocos de um circuito integrado muito comum da família TTL. A tabela 9.1 apresenta as especificações do circuito integrado TTL 7400 (4 portas NE de 2 entradas na versão padrão).

Concluímos pelos resultados que à saída deste bloco, poderemos ligar no máximo outros 10, ou seja, 10 terminais de entrada de blocos similares.

Tempo de Atraso de Propagação

O tempo de atraso de propagação (propagation delay time) é definido como o tempo que um bloco lógico leva para mudar de estado deste a aplicação de um nível lógico para tanto. Em outras palavras, é o tempo que um bloco leva para responder, ou seja, passar do estado 1 para o estado 0 ou vice-versa. Na prática, em terminologia de manuais, o tempo de atraso de propagação quando vai do nível 0 para 1, é representado por tPLH (Low to High), e quando vai de 1 para 0 por tPHL (High to Low), e seu valor é da ordem de nanossegundos (ns).

Para ilustrar, a figura 9.2 apresenta um inversor com exemplos de trechos de sinal aplicados à entrada e os respectivos resultados de saída.

Pela figura, considerando que os trechos de sinais da entrada não contenham retardos nas transições de níveis, os de saída, devido a fatores internos do circuito do bloco, irão provocar retardos perceptíveis, acarretando em tempos de atraso.

Esse parâmetro, juntamente com outros, está diretamente relacionado com a velocidade de trabalho do bloco lógico, pois, em regime de chaveamento rápido exigido (alta freqüência), será bastante significativo.

Imunidade ao Ruído

Vamos chamar de imunidade ao ruído, a capacidade que os blocos de determinada família lógica possuem de não receber influências parasitas elétricas ou magnéticas, denominadas ruído, típicas dentro dos sistemas eletrônicos ou sob determinadas condições do ambiente em que estão situados. Existem vários tipos de ruídos que podem agir de diversas formas, porém, em se tratando de níveis lógicos, o ruído pode, principalmente pelo aparecimento de níveis espúrios e indesejáveis, fazer o bloco trabalhar na região de nível indefinido, não executando corretamente a função lógica.

As famílias lógicas possuem um parâmetro denominado margem de imunidade ao ruído, que determina o quanto de tolerância irá haver sobre os limites dos níveis lógicos, sem que haja alteração na sua funcionalidade. Este parâmetro será uma característica típica da família, sendo um item imprescindível na escolha da tecnologia para a confecção de projetos.

Nos itens relativos às famílias TTL e CMOS, abordaremos de forma numérica, estes parâmetros.

Blocos Lógicos Estruturados com Diodos

Antes do estudo das famílias lógicas construídas em circuitos integrados, vamos abordar tópicos referentes à estruturação de circuitos de portas lógicas, utilizando como elementos principais os diodos.

Podemos utilizar diodos como chaves e, devidamente conectados, utilizá-los para a construção dos circuitos das portas E e OU. Este tipo de estruturação é ainda encontrado na prática isoladamente em alguns sistemas digitais específicos, sendo vantajosa sua utilização, principalmente nos casos em que se exige a função lógica com níveis de tensão e corrente de saída superior aos encontrados em circuitos integrados. Convém ressaltar que os circuitos lógicos com diodos não são implementados em circuitos integrados, ficando estes a cargo de outros elementos semicondutores, mais apropriados.

Com diodos, podem ser estruturados apenas os circuitos das portas E e OU, podendo estas operar com níveis de entrada positivos ou com níveis de entrada negativos. Nestes circuitos, na chamada lógica positiva, o nível 1 será um valor positivo de tensão (+Vcc), e na lógica negativa, o nível 1 será

um valor negativo de tensão (-Vcc). Vamos, a seguir, verificar estes circuitos:

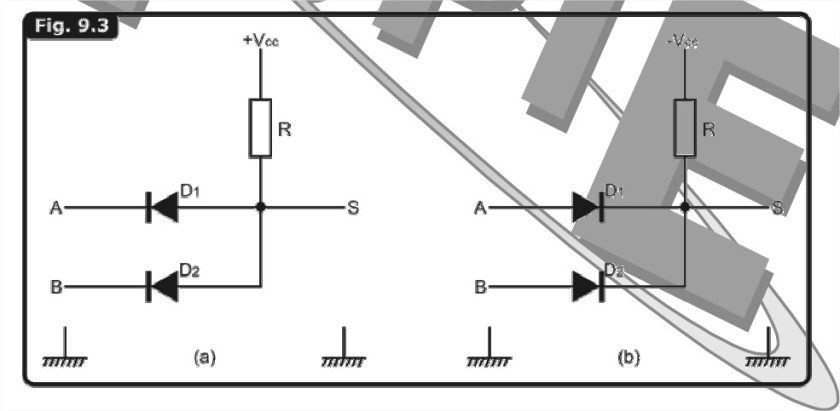

A figura 9.3 apresenta o circuito da porta E com terminais de entrada, estruturado para trabalhar em lógica positiva (a), e em lógica negativa (b).

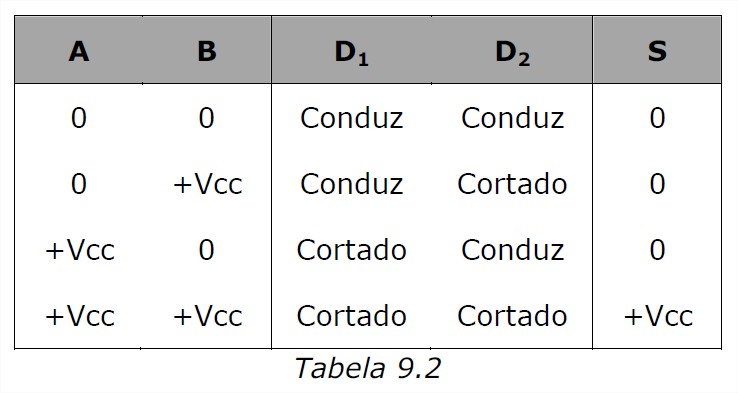

Vamos, a seguir, levantar a tabela da verdade de cada circuito verificando o estado dos diodos em cada caso:

(a) Porta E de lógica positiva (nível 0 = 0 e nível 1 = +Vcc):

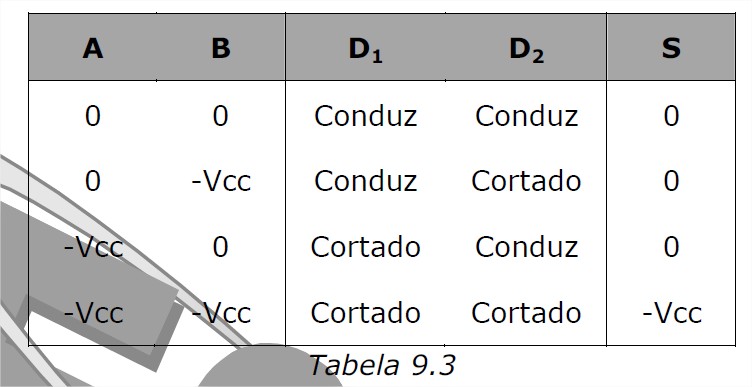

(b) Porta E de lógica negativa (nível 0 = 0 e nível 1 = -Vcc):

Verificando os resultados finais (colunas S), concluímos que os circuitos se comportam como porta E, com saídas compatíveis conforme o tipo de lógica utilizado.

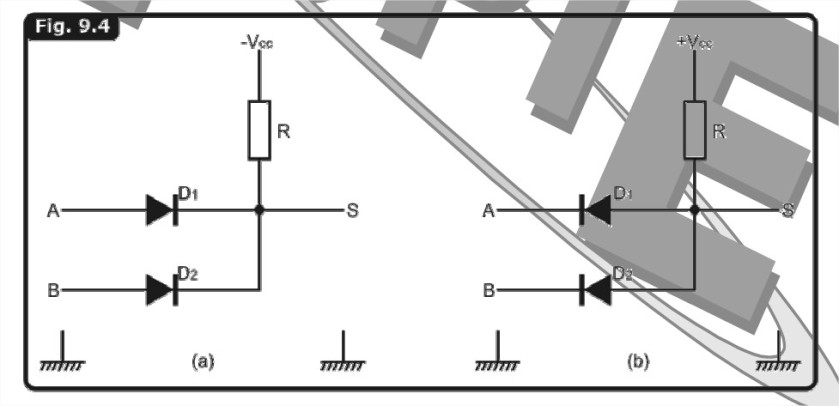

A figura 9.4 apresenta o circuito da porta OU com dois terminais de entrada, estruturado para trabalhar em lógica positiva (a), e em lógica negativa (b).

Podemos notar que o circuito da porta OU de lógica positiva é idêntico ao da E de lógica negativa. A igualdade também ocorre para o da OU de lógica negativa em relação ao da E de lógica positiva.

Através destas observações, concluímos que são apenas dois circuitos, que conforme o tipo de lógica a que estão submetidos, comportam-se como E, ou como OU.

Vamos, da mesma forma, levantar a tabela da verdade de cada um dos circuitos, verificando o estado dos diodos em cada caso:

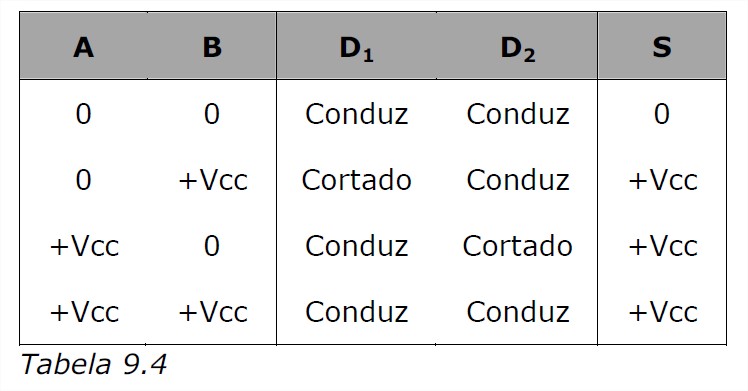

(a) Porta OU de lógica positiva (nível 0 = 0 e nível 1 = +Vcc):

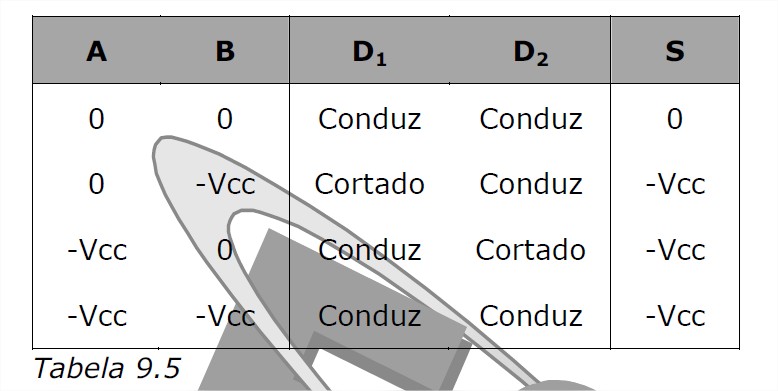

(b) Porta OU de lógica negativa (nível 0 = 0 e nível 1 = -Vcc):

Verificando os resultados finais (Colunas S), concluímos que os circuitos comportam-se como portas OU, com saídas compatíveis conforme o tipo de lógica utilizado.

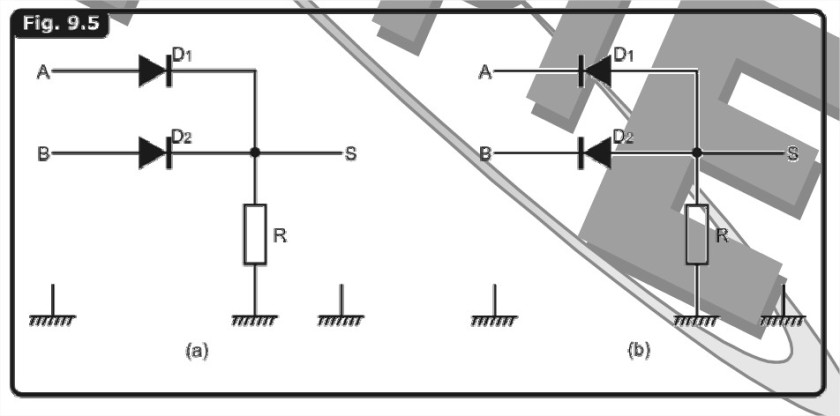

O circuito da porta OU visto, em ambas as lógicas, pode ser simplificado para atuar sem a fonte de alimentação, sendo o nível de saída obtido diretamente, a partir dos níveis aplicados às entradas. A figura 9.5 mostra o circuito da porta OU simplificado para atuar na lógica positiva (a), e na negativa (b).

No circuito da figura 9.5 (a), ao ser aplicado um nível 1 (+Vcc), a qualquer uma ou em ambas as entradas, o respectivo diodo irá conduzir, fazendo surgir na saída S, devida à queda de tensão em R, um nível 1 positivo compatível com a lógica utilizada. O mesmo irá ocorrer com o circuito da figura 9.5 (b), para o nível 1 na lógica negativa (-Vcc). Assim sendo, estes circuitos atuarão como portas OU, dentro das respectivas lógicas, executando a mesma tabela da verdade.

Blocos Lógicos Estruturados em Circuitos Integrados

Conforme já citado, na vida prática, existe disponível toda uma série de circuitos lógicos básicos dispostos em circuitos integrados comerciais pertencentes às famílias TTL e CMOS.

Para a construção destes circuitos, a tecnologia TTL utiliza transistores bipolares, ou seja, comuns de junção NPN ou PNP. Já a tecnologia CMOS utiliza transistores MOS-FET (Metal Oxide Semiconductor Field Effect Transistor) complementares, do tipo N e do tipo P.

A utilização da tecnologia MOS, aqui generalizada, apresenta uma série de facilidades, principalmente nos aspectos construtivos dentro dos circuitos integrados, reduzindo de maneira desta tecnologia (NMOS e PMOS) são utilizadas na implementação de sistemas mais complexos (microprocessadores, memórias de alta capacidade, etc.) de grande quantidade de componentes por chip, chegando hoje em alguns casos, na casa de milhões.

As escalas de integração, ou seja, a faixa relativa ao número de componentes por chip é determinada pela quantidade de portas ou dispositivos ativos dentro do circuito integrado. Estas escalas recebem uma denominação apropriada conforme o número destes elementos existentes internamente. A tabela 9.6 apresenta as escalas de integração com as respectivas densidades expressas em portas por chip.

Os circuitos integrados pertencentes às famílias TTL e CMOS enquadram-se nos níveis de integração SSI e MSI; já os outros sistemas mais complexos, anteriormente citados, enquadram-se nos demais níveis.

Para construir os circuitos internos dos blocos lógicos e assim constituir toda a família lógica, os transistores são dimensionados para atuar como chaves. Vamos, a seguir, estudar o comportamento dos transistores citados, para estruturar os circuitos internos dos blocos lógicos de ambas as famílias.

Transistor Bipolar como Chave

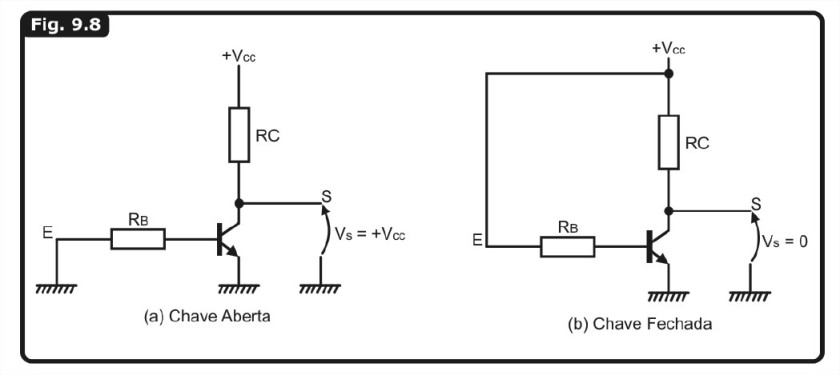

De acordo com a tensão aplicada à base, um transistor bipolar ou comum pode operar no corte ou na saturação, sendo estas duas situações análogas à chave aberta e fechada. O circuito da figura 9.7 mostra a configuração básica de um transistor NPN operando como chave.

De acordo com a tensão aplicada à base, um transistor bipolar ou comum pode operar no corte ou na saturação, sendo estas duas situações análogas à chave aberta e fechada. O circuito da figura 9.7 mostra a configuração básica de um transistor NPN operando como chave.

As situações de corte e saturação são impostas pela polarização, ou seja, são obtidas em função do correto dimensionamento de RC e RB, e pela variação do ponto de trabalho em função da tensão aplicada entre base e emissor do transistor. Para este circuito, o comando da chave será o potencial aplicado à entrada E, ou seja, esta tensão de base.

O transistor comportar-se-á como chave aberta quando aplicarmos um potencial 0 ou negativo na entrada de E. Neste caso, operará na situação de corte, pois estaremos aplicado corrente 0 à sua base, sendo a tensão na saída do circuito igual ao potencial da fonte (+Vcc).

Analogamente, o transistor comportar-se-á como chave fechada quando aplicarmos um potencial positivo nesta mesma entrada. Neste caso, operará na saturação e a tensão entre coletor e emissor cairá para 0.3V no máximo, resultando assim em uma baixa tensão (Vs = 0,3V), sendo considerada como nível 0.

A figura 9.8 ilustra as situações explicadas de corte (a) e de saturação (b) do transistor NPN.

Convém observar que atuando nestas situações, o circuito irá se comportar como um inversor, pois se aplicarmos um nível à sua entrada, este aparecerá complementado na saída.

Utilizaremos estes conceitos para explicar o funcionamento de outros circuitos dentro da família TTL.

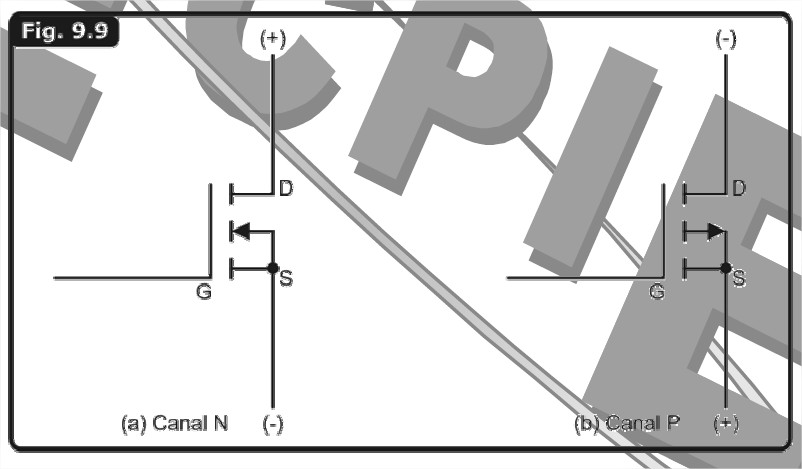

MOS-FET como Chave

Da mesma forma que o transistor bipolar, um MOS-FET pode, conforme a polarização aplicada, atuar como uma chave aberta ou fechada. O princípio consiste em utilizar um MOS-FET do modo indução, e aplicar uma tensão conveniente, conforme o tipo de transistor (canal N ou canal P), entre porta (gate) e fonte (source), obedecendo à polarização aplicada ao terminal dreno (drain). A figura 9.9 apresenta um MOS-FET do tipo canal N (a), e outro do tipo canal P (b) polarizados para atuarem como chaves.

Para o MOS-FET do tipo canal N, inicialmente no estado de alta resistência, se aplicarmos no terminal porta (G), um potencial positivo em relação ao terminal fonte (S), este apresentará uma baixa resistência entre D e S, caracterizando uma condução. Neste caso, o MOS-FET comportar-se-á como chave fechada, fazendo o potencial entre D e S cair para um baixo valor de tensão. Se, no entanto, aplicarmos outro potencial negativo ou nulo, o mesmo se comportará como uma chave aberta, aparecendo entre D e S um alto potencial, ou seja, o da fonte de alimentação (+Vcc). Para ilustrar, a figura 9.10 apresenta estes casos de polarização colocados.

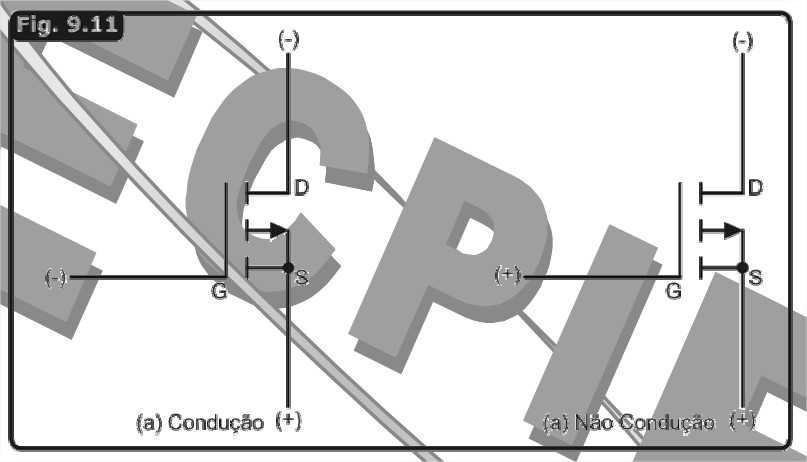

Para o MOS-FET do tipo canal P, inicialmente no estado de alta resistência, se aplicarmos no terminal porta (G), um potencial negativo em relação ao terminal fonte (S) ou nulo em relação ao dreno (mesmo potencial), condução. Neste caso, o MOS-FET comportar-se-á como chave fechada, fazendo o potencial entre D e S cair para um baixo valor de tensão. Se, no entanto, aplicarmos outro potencial positivo em relação ao terminal fonte (S), o mesmo se comportará como uma chave aberta, aparecendo entre D e S um alto potencial, ou seja, o da fonte de alimentação (+VDD). Para ilustrar, a figura 9.11 apresenta estes casos de polarização colocados.

Utilizaremos estes conceitos para explicar o funcionamento dos circuitos básicos da família CMOS.

Família TTL

A família TTL é derivada da antiga família DTL, sendo o resultado de uma série de inovações

tecnológicas. Uma delas é a utilização nos seus circuitos internos de transistores bipolares de vários

emissores, também conhecidos como multiemissores. Trata-se de uma família pioneira, tradicional e

muito utilizada ao longo dos anos, devido principalmente ao seu fácil manuseio, e à colocação no

mercado de uma série de circuitos integrados comerciais e padronizados.

A seguir, vamos analisar um circuito TTL padrão, que utiliza as ligações no estágio de saída

denominadas Active Pull-Up (puxar para cima ativo) e Toten-Pole (em poste), termos estes de difícil

adaptação na tradução. A figura 9.12 apresenta o circuito de uma porta NE TTL.

Autor: Prof. Carlos Alberto Carielo

ECPIE – Escola e Curso Profissionalizante de Informática e Eletrônica

Rua Joaquim Felipe, 119 – Boa Vista – Recife – PE

Fone: 3081-5552

MATRIZ

71

A presença de T3 no coletor caracteriza o Active Pull-Up e sua ligação através do diodo D1 sobre o

coletor de T4, formando um elevador de potencial, o Toten-Pole.

Quando tivermos uma ou ambas as entradas A e B em nível 0, a respectiva junção base-emissor

do transistor T1 irá conduzir levando T2 ao corte por ausência de corrente de base. Conseqüentemente,

pelo mesmo motivo, T4 também será levado ao corte. O transistor T3, por sua vez, estará conduzindo,

pois, por R2 fluirá uma corrente de sua base, e se comportará para a saída como um seguidor de

emissor, fazendo aparecer em S um potencial igual a +Vcc (nível 1).

Quando ambas as entradas estiverem em aberto ou em nível 1, devido ao corte da junção baseemissor

de T1, por R1 fluirá uma corrente que irá saturar T2 e conseqüentemente T4. Devido à elevação

do potencial de base por D1, o transistor T3 estará cortado e ocasionará, na saída, um baixo potencial

equivalente a nível 0.

Transportando estas situações para a tabela da verdade, notaremos que o circuito funcionará

como uma porta NE, sendo padrão nesta família.

A B S

0 0 1

0 1 1

1 0 1

1 1 0

Tabela 9.7

Convém ressaltar que, nesta família, a entrada em aberto equivale a nível lógico 1.

Outra observação é que tanto na situação de nível 0 ou 1 de saída o bloco estará apto a fornecer

o nível a um terminal de entrada de outro bloco TTL, sendo respeitados os parâmetros VIL e VIH. Na

situação de nível 0 de saída, em especial, a compatibilidade será obtida através da condução de T4, pois

pelo coletor fluirá a corrente proveniente da entrada do bloco seguinte, funcionando T4 como receptor de

corrente, sendo por este motivo denominado transistor Pull-Down (puxar para baixo), outro termo de

difícil tradução.

9.5.1 Características Gerais e Parâmetros da Família TTL

Os circuitos TTL são produzidos em duas séries comerciais: a série 74XXX e 54XXX, sendo esta

última denominada série militar ou profissional, devido à maior margem de variação nas especificações

de alimentação e temperatura, assegurando a confiabilidade o desempenho em condições máximas.

Os valores lidos em manuais são valores dos diversos parâmetros para uma tensão de

alimentação de 5V a 25ºC. As especificações da série comum (74XXX) devem garantir esse

funcionamento com 5% de tolerância numa faixa de temperatura de 0ºC a 70ºC. Já as especificações da

série militar (54XXX) garantem o funcionamento com 10% de tolerância numa faixa de temperatura de

-55ºC a 125ºC.

Vamos agora, enumerar os principais parâmetros encontrados nos manuais em nomenclaturas

originais:

Autor: Prof. Carlos Alberto Carielo

ECPIE – Escola e Curso Profissionalizante de Informática e Eletrônica

Rua Joaquim Felipe, 119 – Boa Vista – Recife – PE

Fone: 3081-5552

MATRIZ

72

1 – Alimentação (Vcc): Na família TTL, temos para todos os blocos uma alimentação de 5V.

Para a série 54 temos Vcc mínimo = 4,5V e Vcc máximo = 5,5V que são valores dentro da especificação

militar de 10% de tolerância. Para a série 74, temos Vcc mínimo = 4,75V e Vcc máximo = 5,25V que são

valores dentro da especificação comum de 5% de tolerância.

2 – Níveis de entrada e saída, para a versão padrão (TTL Standard):

TTL Standard

Parâmetros Valores Unidade

VIL 0,8 V

VOL 0,4 V

VIH 2,0 V

VOH 2,4 V

IOL 16 mA

IIL 1,6 mA

IOH 400 μA

IIH 40 μA

Tabela 9.8

3 – Fan-Out: Na versão padrão, o Fan-Out é igual a 10 (ver exemplo de cálculo no item 9.2.2),

ou seja, podemos ligar à saída deste bloco no máximo outros 10 blocos similares. Este valor,

normalmente, é generalizado para toda a família TTL.

4 – Tempo de atraso de propagação: Este parâmetro varia conforme a versão utilizada, sendo

o valor médio aproximado da ordem de 10ns na versão mais comum. A tabela 9.9 apresenta os tempos

de atrasos típicos de subida tPLH (Low to High), e de descida tPHL (High to Low), para esta versão.

TTL Standard

Parâmetros V. Típico Unidade

tPLH 11 ns

tPHL 7 ns

Tabela 9.9

5 – Imunidade ao Ruído: A margem de imunidade ao ruído especificada para a família TTL de

maneira geral, é obtida supondo a ligação da saída de um bloco para a entrada de outro, sendo definida

por aquela margem de segurança colocada pelo fabricante entre os parâmetros de entrada e saída. É

calculada pela diferença dos parâmetros relativos a esses níveis de tensão (margem de imunidade ao

ruído DC). Assim sendo, temos:

No nível 1: UVRH = VOH (mín.) – VIH (mín.) = 2.4 – 2,0 = 0,4V

No nível 0: UVRL = VIL (máx.) – VOL (máx.) = 0,8 – 0,4 = 0,4V

∴ UVR = 0,4V

A margem de imunidade ao ruído para a família TTL, de maneira geral, é igual a 0,4V, e é

considerada baixa em relação à família CMOS, sendo os componentes CMOS mais apropriados para

operar frente a situações de alto nível de ruído.

6 – Potência Dissipada: O consumo médio de potência da família TTL é da ordem de 10mW por

porta na versão mais comum.

9.5.2 Tipos de Blocos da Família TTL

A família TTL, através de suas séries, colocou blocos disponíveis no mercado de componentes,

com muitas possibilidades. Entre, eles, vamos destacar blocos open-collector, tri-state e schimitttrigger.

Autor: Prof. Carlos Alberto Carielo

ECPIE – Escola e Curso Profissionalizante de Informática e Eletrônica

Rua Joaquim Felipe, 119 – Boa Vista – Recife – PE

Fone: 3081-5552

MATRIZ

73

9.5.2.1 Open-Collector

A família TTL possui blocos lógicos com construção em open-collector (coletor aberto). Os

circuitos destes blocos são semelhantes aos dos blocos convencionais, com a única diferença de não ter

internamente o resistor de coletor ligado ao +Vcc. Este deve ser ligado externamente quando da

utilização do bloco. O circuito interno de uma porta NE TTL open-collector é visto na figura 9.13.

Esta configuração permite o controle externo da corrente de coletor, proporcionando inclusive o

aumento do Fan-Out. Além disso, permite a ligação conjunta de várias saídas através de um único

resistor de coletor, formando uma ligação denominada E por fio (Wired-And), pois executa a função de

porta E, apenas com ligação. A figura 9.14 mostra a ligação, a tabela e a simbologia utilizadas para se

obter uma função E através de blocos open-collector.

S1 S2 S

0 0 0

0 1 0

1 0 0

1 1 1

Tabela 9.10

Notamos pela figura, que o nível 0 é obtido pela saturação de cada transistor ou por ambos,

conforme a função lógica de cada bloco, sendo a respectiva corrente de coletor fornecida pelo mesmo

resistor colocado externamente. O nível 1 é obtido pelo corte de ambos.

Como outra aplicação, podemos citar o uso muito comum de saídas open-collector para ativar

displays de 7 segmentos a led, possibilitando o controle de luminosidade pelo resistor de coletor

calculado e colocado externamente.

Autor: Prof. Carlos Alberto Carielo

ECPIE – Escola e Curso Profissionalizante de Informática e Eletrônica

Rua Joaquim Felipe, 119 – Boa Vista – Recife – PE

Fone: 3081-5552

MATRIZ

74

9.5.2.2 Tri-state

Conforme já visto, existem blocos que apresentam um terceiro estado de saída (tri-state)

caracterizado por uma alta impedância.

Para ativar o tri-state (também utilizamos: 3-state ou three-state), o bloco específico possui

um terminal que, conforme o nível lógico assumido faz a saída permanecer ou não em alta impedância.

Para ilustrar esta possibilidade a figura 9.15 mostra o circuito simplificado de uma porta NE TTL de duas

entradas com saída tri-state.

No circuito, se aplicarmos nível 1 ao terminal de entrada de controle da saída (G) ou o deixarmos

em aberto, o circuito funcionará normalmente como uma porta NE, pois D2 e D3 estarão cortados. Se, no

entanto, aplicarmos nível 0, devido à respectiva condução de corrente pelos mesmos diodos, os pontos

X1 e X2 cairão para baixos potenciais, levando T2, T3 e T4 para a situação de corte. O terminal de saída,

neste caso, será praticamente desligado do circuito, ocasionando o estado de alta impedância.

Na família TTL, as saídas tri-state são encontradas fazendo parte de vários dispositivos, porém,

isoladamente como portas, estão disponíveis apenas em buffers comuns e inversores.

As aplicações de dispositivos com saídas tri-state são muitas principalmente em sistemas com

microprocessadores, onde vários circuitos integrados utilizam o mesmo conjunto de fios de forma

compartilhada formando assim a já conhecida via de dados do sistema.

9.5.2.3 Schimitt-Trigger

São também encontrados disponíveis na família TTL, blocos configurados com entradas Schimitt-

Trigger (gatilho de Schimitt). Este tipo de bloco possibilita tornar rápidas, as variações lentas dos níveis

de tensão de determinados sinais aplicados à sua entrada, causando na saída o aparecimento de uma

onda quadrada bem-definida. Em outras palavras, este tipo de bloco, além de realizar sua função lógica,

quadra o sinal aplicado à entrada, desde que sejam respeitados os parâmetros mínimos e máximos de

tensão especificados para o bloco.

O Bloco irá considerar iguais a 0, os valores de entrada abaixo do especificado por VT –

(Negative-Going Threshold Voltage) ou limiar negativo de tensão, e irá considerar iguais a 1, os

valores acima de VT + (Positive-Going Thereshold Voltage) ou limiar positivo de tensão.

Para ilustrar, a figura 9.16 apresenta um inversor TTL Schimitt-trigger (a) e a ação sobre um

sinal de variação lenta aplicado à sua entrada (b).

Autor: Prof. Carlos Alberto Carielo

ECPIE – Escola e Curso Profissionalizante de Informática e Eletrônica

Rua Joaquim Felipe, 119 – Boa Vista – Recife – PE

Fone: 3081-5552

MATRIZ

75

O símbolo (histerese) presente no inversor é utilizado em manuais de fabricantes para

identificar as portas que executam a função de Schimitt-trigger, sendo atribuído devido à aparência da

característica de transferência do bloco. Para exemplificar esta curva e os valores práticos dos

parâmetros VT – e VT +, a figura 9.17 mostra a característica de transferência típica do circuito integrado

TTL 7414 (6 inversores Schimitt-trigger).

Pelo gráfico, notamos que para a saída assumir nível 0 (VOL = 0,2V), é necessário que a variação

de entrada atinja aproximadamente VT + = 1,4V, e que para assumir nível 1 (VOH = 3,4V), é necessário

que a variação de entrada caia abaixo de VT – = 0,9V aproximadamente.

Os dispositivos Schimitt-trigger são largamente utilizados em sistemas digitais, para transformar

em onda quadrada as variações oriundas de sistemas analógicos diversos não compatíveis. Uma dessas

aplicações consiste em a partir de uma amostra da tensão senoidal da rede elétrica, obter o sinal de clock

quadrado de 60Hz para, após dividido, fornecer 1Hz aos contadores de segundos dos relógios digitais.

Além de inversores, são encontradas disponíveis em circuitos integrados da família TTL, portas

NE Shimitt-trigger.

9.5.3 Versões dos Circuitos TTL

Além dos blocos comuns (Standard), a família TTL possui outras versões de circuitos com a

finalidade de atender a solicitações de ordem prática nos parâmetros relativos à velocidade e consumo de

potência. A tabela 9.11 apresenta um quadro comparativo entre estas outras versões e as respectivas

identificações.

Versão

Identificação

da série

Tempo de

atraso de

propagação

típico por

porta

Consumo

de

potência

por

porta

Freqüência

de clock

máxima

para flipflop

Observações

Standard 54/74 10 ns 10 mW 25 MHz Comum

Low

Power 54L/74L 33 ns 1 mW 3 MHz

Baixíssimo

consumo

High

Speed

54H/74H 6 ns 22 mW 50 MHz Alta

velocidade

Schottky 54S/74S 3 ns 19 mW 125 MHz

Altíssima

velocidade

Advanced

Schottky 54AS/74AS 1,5 ns 8,5 mW 200 MHz

Altíssima

velocidade e

baixo

consumo

Low

Power

Schottky

54LS/74LS 10 ns 2 mW 45 MHz Baixíssimo

consumo

Advanced

Low

Power

Schottky

54ALS/74ALS 4 ns 1 mW 70 MHz

Altíssima

velocidade e

baixíssimo

consumo

Tabela 9.11

Autor: Prof. Carlos Alberto Carielo

ECPIE – Escola e Curso Profissionalizante de Informática e Eletrônica

Rua Joaquim Felipe, 119 – Boa Vista – Recife – PE

Fone: 3081-5552

MATRIZ

76

Os valores da tabela são válidos para circuitos integrados de portas NE e servem apenas para

comparações entre as versões, sendo estimados a partir das faixas disponíveis nos manuais comerciais

de diversos fabricantes.

O quadro possibilita a comparação em termos de velocidade e consumo de potência, tomando

como ponto de referência a versão comum, seguida da versão de baixo consumo (L) e de alta velocidade

(H). Essas versões são diferentes entre si devido a alterações introduzidas nos circuitos e nos valores de

seus componentes internos. A partir daí, para as versões do quadro os circuitos apresentam variações

sobre a tecnologia Schottky.

A versão Schottky utiliza em seus circuitos o diodo Schottky, elemento semicondutor construído

com metal de um lado da junção interna para aumentar a velocidade de comutação, que devidamente

colocado entre base e coletor de um transistor, forma um conjunto denominado Transistor Schottky.

Este conjunto, quando utilizado para chaveamento, não atinge a saturação totalmente devido à ligação,

apresentando um tempo de comutação extremamente baixo e conseqüentemente uma altíssima

velocidade de trabalho. A figura 9.18 mostra a ligação de um diodo Schottky em um transistor bipolar

para formar o referido conjunto (a) e a simbologia utilizada para este (b).

As alterações introduzidas nos circuitos e nos valores dos componentes produziriam em relação à

versão Schottky (S), uma variação de menor consumo (LS), e nas versões Schottky Avançadas (AS e

ALS), uma grande melhora no desempenho total, principalmente no produto velocidade-consumo

constituindo-se nos menores entre todas as versões existentes.

9.5.4 Circuitos Integrados TTL

A família TTL colocou no mercado uma série de circuitos integrados padronizados com

configurações de pinagens disponíveis nos manuais dos fabricantes. São circuitos integrados de 14 pinos

ou mais, conforme a complexidade do circuito agregado, com encapsulamentos denominados DIP (Dual-

In-Line Package), cuja identificação da disposição dos terminais se faz através da vista superior, em

sentido anti-horário, a partir do ponto de referência colocado no pino 1, próximo ao chanfro existente no

bloco. Para exemplificar, a figura 9.19 apresenta a pinagem do circuito integrado 7400 (4 NE com 2

entradas), sendo esta válida também para o 5400 e, ainda, para as versões 74L00, 74H00, 74S00,

74AS00, 74LS00, 74ALS00.

Autor: Prof. Carlos Alberto Carielo

ECPIE – Escola e Curso Profissionalizante de Informática e Eletrônica

Rua Joaquim Felipe, 119 – Boa Vista – Recife – PE

Fone: 3081-5552

MATRIZ

77

9.6 Família CMOS

A outra família de extrema importância a ser abordada é a CMOS (Complementary MOS). Tratase

de uma família que tem seus circuitos construídos por transistores MOS-FET complementares do tipo

canal N e canal P. Suas configurações básicas permitem obter-se uma série de vantagens, tais como: alto

Fan-Out, alta margem de imunidade ao ruído e baixíssimo consumo, sendo esta uma de suas mais

importantes características.

Vamos, a seguir, analisar o funcionamento dos blocos lógicos principais desta família que são as

portas NOU e NE. A figura 9.20 mostra o circuito básico de uma porta NOU CMOS.

Quando ambas a entradas estiverem em 0 (potencial do terra), os MOS-FET cal P, M1 e M2

estarão conduzindo e os MOS-FET canal N, M3 e M4 estarão cortados. Isso fará com que a tensão de saída

assuma valor igual a +VDD (nível 1). Quando pelo menos uma das entradas estiver em +VDD (nível 1),

teremos o respectivo MOS-FET canal N, M3 ou M4 conduzindo, fazendo com que na saída tenhamos uma

tensão igual a 0. Transpondo estas situações para uma tabela verdade, concluímos que o circuito

comporta-se como uma porta NOU:

A B S

0 0 1

0 1 0

1 0 0

1 1 0

Tabela 9.12

Vamos analisar agora, o funcionamento da porta NE CMOS. O circuito básico é visto na figura

9.21.

Autor: Prof. Carlos Alberto Carielo

ECPIE – Escola e Curso Profissionalizante de Informática e Eletrônica

Rua Joaquim Felipe, 119 – Boa Vista – Recife – PE

Fone: 3081-5552

MATRIZ

78

Quando pelo menos uma das entradas estiver em 0, o respectivo MOS-FET canal N, M3 ou M4

estará cortado e o respectivo MOS-FET canal P, M1 ou M2 estará conduzindo, logo, teremos na saída uma

tensão igual a VDD (nível 1). Quando ambas as entradas estiverem em +VDD (nível 1), tanto M3 como

M4 estarão conduzindo, ficando M1 e M2 cortados, logo, teremos na saída uma tensão igual a 0.

Transpondo estas situações para uma tabela verdade, concluímos que o circuito comporta-se como uma

porta NE:

A B S

0 0 1

0 1 1

1 0 1

1 1 0

Tabela 9.13

Convém ressaltar que a partir destes circuitos básicos o fabricante pode estruturar, internamente

no circuito integrado, qualquer outro bloco mantendo as mesmas características de entrada e saída.

Outro ponto importante a ser ressaltado é que ao contrário da família TTL, não é aconselhável

deixar terminais de entrada em vazio nas portas CMOS, pois nesta situação, estes e tornam susceptíveis

à captação de carga estática e ruídos indesejáveis, causando pela polarização errônea dos dispositivos,

um aumento da dissipação de potência e consequente sobreaquecimento. Os terminais não utilizados

devem ser conectados conforme o caso da função lógica envolvida, ao terra ou VDD do circuito.

9.6.1 Características Gerais e Parâmetros da Família CMOS

A família CMOS possui circuitos integrados disponíveis nas séries comerciais 4000A, 4000B e

54/74C, sendo esta última semelhante à TTL na pinagem dos circuitos integrados e função dos blocos

disponíveis. Além destas, a família CMOS também possui versões de alta velocidade e melhor

desempenho: 74HC/74HCT (High-speed CMOS), sendo HCT especialmente desenvolvida para atuar

com parâmetros de tensões compatíveis com TTL-LS, e as apropriadas para operar com baixa tensão de

alimentação: 74LV/74LVC (Low Voltage CMOS).

Os circuitos integrados CMOS são dimensionados para operar na faixa de temperatura de -40ºC a

+85ºC nas séries comuns, e nas variações de uso profissional (militar) na faixa de -55ºC a +125ºC.

Vamos agora, enumerar os principais parâmetros encontrados nos manuais em nomenclaturas

originais:

1 – Alimentação (VDD): Quanto à tensão de alimentação, esta família permite para as séries

4000 e 74C operarem na faixa de 3V a 15V, para a versão HC de 2V a 6V e para HCT de 4,5V a 5,5V.

Autor: Prof. Carlos Alberto Carielo

ECPIE – Escola e Curso Profissionalizante de Informática e Eletrônica

Rua Joaquim Felipe, 119 – Boa Vista – Recife – PE

Fone: 3081-5552

MATRIZ

79

Para as séries de baixa voltagem, a faixa de 1V a 3,6V para LV e 1,2V a 3,6V para LCV, sendo estas

especialmente projetadas para operar com 3,3V, tensão típica de vários sistemas atuais.

Podemos notar que esta família e suas versões apresentam a vantagem de possuir uma larga

faixa de tensão de alimentação, não necessitando de regulagem precisa na fonte como no caso da TTL.

2 – Níveis de tensões e correntes de entrada e saída: Os blocos da família CMOS apresentam

estes níveis, especificados nos manuais, com variações em função da versão e tipo de bloco utilizado. De

maneira geral, apresentam nas entradas, valores de VIL (máx.) iguais a 30% do VDD e VIH (min.) iguais a

70% do VDD, com exceção da versão HCT que possui estes nível igual a TTL-LS. Nas saídas dos blocos,

devido principalmente à baixa absorção de corrente na ligação com o bloco seguinte (alta resistência de

entrada), apresentam valores muito próximos a 0 (VOL máx.) e VDD (VOH min.). A tabela 9.14 apresenta

os valores de tensões e correntes para a série 4000B, operando com VDD igual a 5V.

CMOS 4000B

Parâmetros Valores Unidade

VIL 1,5 V

VOL 0,05 V

VIH 3,5 V

VOH 4,95 V

IOL 0,4 mA

IIL 1 μA

IOH 0,4 mA

IIH 1 μA

Tabela 9.14

3 – Fan-Out: Nesta família, de modo generalizado, o Fan-Out é igual a 50, porém varia

conforme as versões empregadas. Este valor considerável é devido principalmente à pouca deriva da

corrente de saída, em função da alta resistência de entrada dos dispositivos CMOS conectados, sendo a

limitação causada pela ação das capacitâncias de entrada dos blocos subseqüentes somados. Devido à

compatibilidade de algumas versões com TTL, é comum nos manuais, encontrar este parâmetro definido

para um carregamento da saída com TTL-LS, sendo este um menor valor (Fan-Out = 10 para HC/HCT).

4 – Tempo de atraso de propagação: Nas séries mais comuns, o tempo de atraso de

propagação médio é da ordem de 90ns, constituindo-se em uma grande desvantagem. O problema foi

superado com o aparecimento das versões apropriadas para uso em alta velocidade (HC/HCT), com

parâmetros compatíveis com os das versões TTL para a mesma finalidade. Para exemplificar, a tabela

9.15 apresenta os parâmetros de velocidade para a série básica e as versões citadas, com tensão de

alimentação igual a 5V.

Versão

Tempo de atraso

de propagação

típico por porta

Freqüência de

clock máxima

para flip-flop

4000B 90 ns 10 MHz

HC/HCT 8 ns 55 MHz

Tabela 9.15

5 – Imunidade ao Ruído: A margem de imunidade ao ruído para a família CMOS é igual a 45%

de VDD, sendo muito alta se comparada a família TTL. Devido a isso, estes blocos são adequados para

serem utilizados em circuitos que operam em sistemas ou ambientes de alto nível de ruído.

6 – Potência Dissipada: O consumo de potência da família CMOS (com VDD = 5V) é da ordem

de 1nW por porta série 4000 e 2,5 nW por porta na versão 74HC, sendo estes valores muito baixos,

caracterizando-se em mais uma grande vantagem desta família.

7 – Manuseio: A família CMOS, ao contrário da TTL, possui problemas com o manuseio dos

circuitos integrados que devido à ação da eletricidade de estática, provoca a degradação das junções

internas dos chips, comprometendo sua vida útil. A danificação total do bloco pode só acontecer após

certo tempo de uso, causando sérios transtornos ao fabricante do sistema no qual o componente está

engajado.

Para contornar o problema, possibilitando um manuseio mais seguro, existe no mercado uma

série de dispositivos antiestáticos (pulseiras de aterramento, pisos, borrachas de bancadas, estações de

Autor: Prof. Carlos Alberto Carielo

ECPIE – Escola e Curso Profissionalizante de Informática e Eletrônica

Rua Joaquim Felipe, 119 – Boa Vista – Recife – PE

Fone: 3081-5552

MATRIZ

80

solda, etc.), sendo inclusive os circuitos integrados comercializados em embalagens com isolação

apropriada.

As versões mais recentes desta família possuem internamente nas entradas e saídas dos blocos,

diodos de proteção para evitar a ação da eletricidade estática, porém, aconselha-se seguir da mesma

forma as normas de manuseio apropriadas.

9.6.2 Circuitos Integrados CMOS

Da mesma forma que na TTL, a família CMOS colocou no mercado uma série de circuitos

integrados padronizados com configurações de pinagens disponíveis nos manuais dos fabricantes. Para

exemplificar, a figura 9.22 apresenta a pinagem do circuito integrado 4001B (4 NOU com 2 entradas) e

do 74HC04/74HCT04 (6 inversores), sendo estes últimos de mesma pinagem que o 7404 da família TTL